Physical Design Mentorship

Why PD?

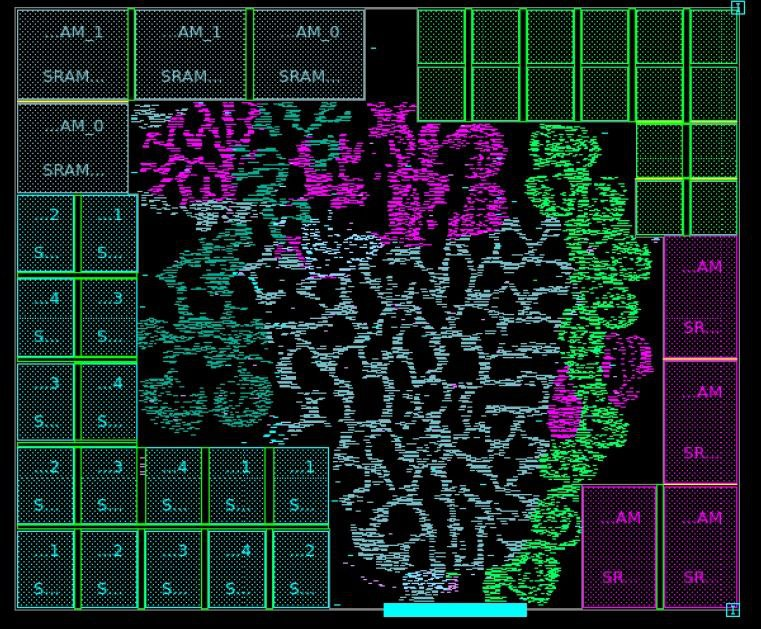

Physical Design is conversion of a set of gates connected through nets (netlist) to a layout form in a given chip area meeting aspects of power, area, performance (STA) honouring time to market. Floorplan, placement of cells, clock building, routing of metals connecting the logic gates and meeting the desired timing frequency is the goal of Physical Design.

Course overview - PD

20 weeks program |

|

Program covers all aspects of RTL to GDSII flow (refer syllabus for integrated) |

|

Every topic and sub-topic covers industry oriented practical aspects |

|

Every topic and sub-topic is taught with hands-on lab from RTL to GDSII |

|

In depth coverage of topics like Advanced Digital Design, CMOS, PnR flow, Pre-Layout STA and Sign-Off STA, Physical Verification, Low Power Methodologies, Logic Equivalence Check and TCL Scripting are key differentiators in the program |

|

Curriculum and projects are co-developed with inputs from Industry experts |

|

Soft skill training on the fly during the sessions |

|

Resume preparation guidance |

|

Regular assessment of areas where program members need improvement |

|

Thorough in depth learning by interlinked theory and labs in parallel |

|

Course completion certificate after completion of program |

|

Trainers and Mentors available anytime for discussion |

|

Path to VLSI industry will be clear once this program is completed |

|

Labs can be accessed 24x7 through VPN from anywhere |